Nyheder

DAC udforsker AI og ML's rolle på tværs af markederne

Moscone Center, San Francisco, vil være vært for DAC 25-28 juni

OneSpin Solutions og Austemper Design Systems vil både fremhæve værktøjer til funktionel sikkerhedskontrol. Austemper vil fokusere på missionskritisk systemudvikling, med KaleidoScope-værktøjssuppen, der understøtter analog design for samtidig fejlspredning i blandet signal. Den automatiserede værktøjssuite har sikkerhedsanalyse, syntese og verifikationsfunktioner til certificeringsorienterede applikationer. Den bruges til storskala automobildesigner i ADAS og autonom kørsel. Den samtidige fejl simulering omfatter simuleringer anbefalet af ISO 26262 for at overholde ASIL krav.

Virksomheden samarbejdede for nylig med OneSpin Solutions for at vedtage en værktøjsstøttet metode til funktionelle sikkerhedsapplikationer, der kombinerer et design- og verifikationsflow, som vil blive demonstreret på OneSpin-kabinen. Hardware sikkerhed mekanismer indsættes i chip design og OneSpin Solutions 'værktøjer formelt verificere hardware sikkerhedslogik. Ækvivalens kontrol sikrer, at den indsatte sikkerhedslogik ikke påvirker den normale funktionalitet, og fejldetekteringsanalysen verificerer, at sikkerhedsmekanismer fungerer korrekt i tilfælde af tilfældige fejl.

OneSpin fremmer også sit værktøjskvalifikationskit, efter TÜV SÜDs verifikation af dets udviklingsprocesser. Det oprindelige kit er tilgængeligt for virksomhedens 360 EC-FPGA EDA værktøj, en automatisk sekventiel ækvivalens kontrol, der forhindrer FPGA designstrømme fra at introducere implementeringsfejl. Sættet er certificeret til ISO 26262, IEC 61508 og EN 50128.

FPGA indsigter

Stadig med FPGA design, Plunify har samarbejdet med Xilinx for at tilbyde Vivado design suite i skyen via Plunify Cloud platformen. Designere betaler så lidt som 50c for at udarbejde et Vivado-projekt på Amazon Web Services (AWS) skyen, herunder licenser.

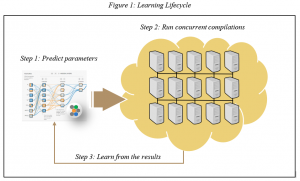

Virksomheden vil også vise forbedringer af sin InTime timing-lukning software til optimering af FPGA timing i skyen (Figur 1). InTime Optimization Metodology kan forbedre klokfrekvensen med 20 til 80% og opfylde timing krav i dage, snarere end uger via maskinindlæring. Softwaren accelererer også timing lukning og optimering og er tilgængelig via skyen.

Virksomheden vil også vise forbedringer af sin InTime timing-lukning software til optimering af FPGA timing i skyen (Figur 1). InTime Optimization Metodology kan forbedre klokfrekvensen med 20 til 80% og opfylde timing krav i dage, snarere end uger via maskinindlæring. Softwaren accelererer også timing lukning og optimering og er tilgængelig via skyen.

Fremme af eFPGA teknologi, Achronix Semiconductor samarbejder med IP-specialist CAST at øge gennemstrømningen og gøre besparelser i hukommelsesopbevaring.

De to udstillere vil forklare, hvordan CAST's lossless compression IP er blevet portet til Achronix FPGA porteføljen til brug i data center og mobile edge dataoverførselsapplikationer. Hardware implementeringen af den tabløse komprimeringsstandard for Deflate, GZIP og ZLIB er kompatibel med software implementeringer, der anvendes til komprimering eller dekompression for at give op til 100 Gbit / s gennemstrømning med lav kompression og lav latens, kombineret med Speedcore eFPGA teknologi til at flytte og opbevare store data ved lavt strømforbrug.

CAST har porteret sin IP til Achronix FPGA'er

Energieffektivitet

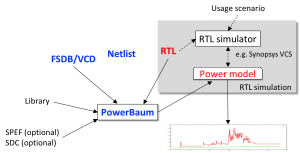

Taler om strømstyring, en anden udstiller, Baum, identificerer energieffektivitet som det mest underudviklede område i chipdesign. Dens automatiske effektanalyse og modelleringsværktøj er designet til automotive, IoT, mobile, netværk og server projekter. PowerBaum 2.0 (Figur 3) understøtter dynamisk og statisk strøm, idet RTL og netlist beskrives, og tilføjer støtte til strømanalyse med hardwareemulering. Dette siger firmaet, giver ingeniører mulighed for at rette strømbugs i realistiske software scenarier. Værktøjet understøtter også analyse med vilkårlige temperaturer, som er angivet af designere, for at vurdere temperaturens virkninger på et designs strømforbrug.

På DAC vil selskabet også introducere PowerWurzel, en gate-niveau strømanalysemotor, der skal integreres med PowerBaum til strømmodellering.

Figur 3 Baums værktøjer analyserer energieffektivitet

Cloud-baserede SoC design og verifikationsværktøjer til IC design fra Metrics inkludere Cloud Simulator og Verification Manager, designet til at håndtere simulationskrav og ressourcer, justere dem op eller ned hvert minut. Virksomheden hævder, at Google Cloud muliggør ubegrænset UVM-kompatibel SystemVerilog-simuleringskapacitet og indfødt, webbaseret verifikationsstyring til hurtigere regressionstider, reducerede kodeordfejl og forudsigelig kodedækning.

Bortset fra udstillere arrangerer arrangementet tekniske sessioner og et program af keynoter, der adresserer aktuelle områder. I år vil Cadence være vært for en vejledning om funktionel sikkerhed og pålidelighed for automotive applikationer, og en om maskinindlæring ('Maskinindlæring tager talegenkendelse ydeevne til næste niveau'). Et keynote af Anna-Katrina Shedletsky, Instrumental, vil mandag den 25. juni fokusere på 'Automatisering Intelligence: Maskinindlæring og Fremtidens Fremstilling'. Brug af ML og AI til socialhjælpebasik (SAR) udforskes i torsdagens hovedtal af Maja Matarić, Universitetet i Sydlige Californien, som vil præsentere "Automation vs Augmentation: Socially Assistive Robotocs og Work Future".

En anden keynote fortaler RISC-V som et middel til at frigøre arkitekter fra ejendomsrettede instruktionssæt-arkitekturer (ISA'er). David A Patterson, Google og University of California, vil præsentere 'En ny gylden tidsalder for computerarkitektur: Domain Specific Accelerators og Open RISC-V'.

Et nyt område i år på DAC er Design Infrastructure Alley. Initiativet fra ESD Alliance og Association for højtydende computere er et område dedikeret til it-infrastrukturen til design af elektroniske systemer og komponenter. Ud over computerkrav og opbevaringskrav til design og styring af skyens brug er der en dedikeret design-on-the-cloud pavillionsteater, der diskuterer licenshåndtering, netværksberegning og datasikkerhed.